IBM reduce a 5 nanómetros el tamaño de los transistores para los chips del futuro

A esta escala, habría espacio para 30.000 millones de transistores en un microchip del tamaño de una uña

Un grupo de investigadores de IBM, junto con equipos de Global Foundries y Samsung, ha desarrollado un nuevo proceso industrial de fabricación que permitirá fabricar transistores y chips a una escala clave de 5 nanómetros (nm) en unos años, reduciendo aún más las escalas más avanzadas de 7 y 10 nm, que ya son posibles, y que pronto serán las más comunes.

Esto supone un nuevo avance en la confirmación de la ley de Moore, propuesta por el ingeniero que fundó Intel allá por 1965. Básicamente, afirma que la capacidad de procesamiento de los chips se multiplicaría al tiempo que su tamaño se iría reduciendo cada cierto número de meses (originalmente, cada dos años). Aunque hay límite absoluto a esta ley empírica –el tamaño de los átomos– hasta ahora se ha cumplido de forma bastante aproximada. Y los ingenieros parecen querer hacerla durar más todavía.

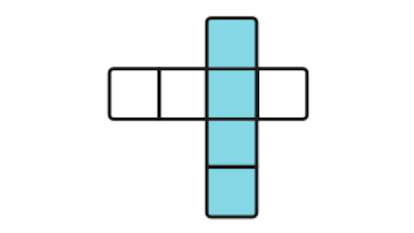

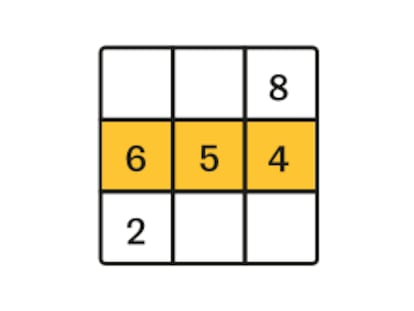

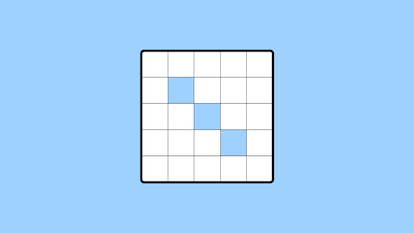

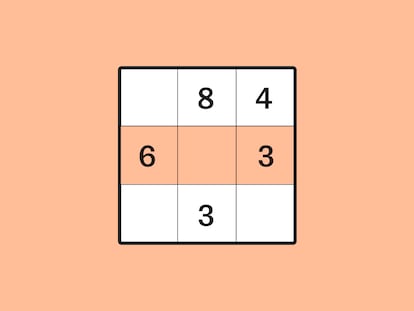

El avance logrado por IBM ha sido posible gracias a la utilización de lo que se denominan nanoláminas de silicio, que sustituyen a la tecnología FinFET (tridimensional) común hoy en día (para chips de 7 y 10 nm). A las nanoláminas se les aplica un proceso de grabación mediante litografía denominado "ultravioleta extrema" (EUV) que dibuja todos transistores del chip sin necesitar tanto espacio de separación como otras. De este modo se pueden empaquetar hasta 30.000 millones de transistores en un solo chip del tamaño de una uña, frente a los 20.000 millones como máximo que permitía la tecnología de 7 nm.

Aunque ya se había ha demostrado la posibilidad de fabricar transistores más pequeños –como los de 1 nanómetro por parte de investigadores del Lawrence Berkeley National Laboratory– en esos casos la utilización de nuevos materiales (el disulfuro de molibdeno) todavía distaba de poder convertirse en un proceso industrial como los actuales. La fabricación de chips de IBM de 5 nm en cambio, con ideas que la compañía lleva una década poniendo en práctica, podría estar tan cerca como "unos pocos años", según ha afirmado los investigadores, que manejan fechas tentativas como 2020.

¿Qué ventajas suponen estos chips tan pequeños?

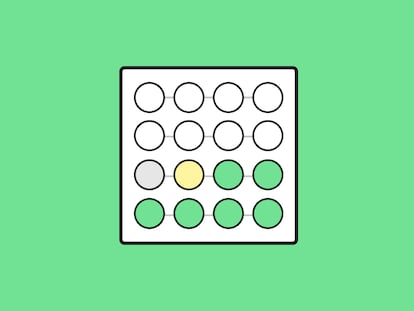

Aparte de la lógica miniaturización al poder comprimir más transistores en menos espacio (hasta un 40 por ciento), también está el ahorro de energía (hasta un 75 por ciento), algo cada vez más importante de cara a su utilización en dispositivos móviles como teléfonos, tabletas, relojes o wearables. Según explican, estos chips permitirían no tener que recargar el móvil nada más que una vez cada dos o tres días.

Aparte de esto, el poder contar con mucha más potencia en pequeños dispositivos gracias a los procesadores más potentes hará que no sean necesarios grandes equipos para disfrutar de aplicaciones en el campo de la inteligencia artificial, la realidad virtual o la llamada "internet de las cosas". ¿Lo más interesante? Que la carrera por la miniaturización no parece detenerse aquí, dado que como parte del anuncio de la tecnología de 5 nm se mencionaron varias veces las palabras "… y más allá".

Tu suscripción se está usando en otro dispositivo

¿Quieres añadir otro usuario a tu suscripción?

Si continúas leyendo en este dispositivo, no se podrá leer en el otro.

FlechaTu suscripción se está usando en otro dispositivo y solo puedes acceder a EL PAÍS desde un dispositivo a la vez.

Si quieres compartir tu cuenta, cambia tu suscripción a la modalidad Premium, así podrás añadir otro usuario. Cada uno accederá con su propia cuenta de email, lo que os permitirá personalizar vuestra experiencia en EL PAÍS.

¿Tienes una suscripción de empresa? Accede aquí para contratar más cuentas.

En el caso de no saber quién está usando tu cuenta, te recomendamos cambiar tu contraseña aquí.

Si decides continuar compartiendo tu cuenta, este mensaje se mostrará en tu dispositivo y en el de la otra persona que está usando tu cuenta de forma indefinida, afectando a tu experiencia de lectura. Puedes consultar aquí los términos y condiciones de la suscripción digital.